130512 / 4AA064 / 6-15

# HPR 400 Transceiver Unit

This document describes the design, theory of operation, and part replacement procedures, of the HPR 400 Transceiver Unit. The unit is used in all the HPR 400 series Hydroacoustic Position Reference (HPR) systems supplied by Kongsberg Simrad AS.

# Document revisions

| Rev | Date     | Written by | Checked by | Approved by |

|-----|----------|------------|------------|-------------|

| Α   | 14.06.94 | NB         | HPJ        | JEF         |

| В   | 16.07.96 | NB         | JW         | JEF         |

| С   | 13.02.98 | NB         | LOS        | JEF         |

| D   |          |            |            |             |

| E   |          |            |            |             |

| F   |          |            |            |             |

| G   |          |            |            | _           |

$(The\ original\ signatures\ are\ recorded\ in\ the\ company's\ logistic\ database)$

II 130512/C

# Contents

| 1 | INTR   | RODUCTION                                      | 1  |

|---|--------|------------------------------------------------|----|

| 2 | GEN    | ERAL INFORMATION                               | 2  |

|   | 2.1 D  | esign                                          | 2  |

|   | 2.2 M  | aintenance actions                             | 2  |

|   | 2.3 Ex | xternal connections                            | 2  |

|   | 2.4 Po | ower supply                                    | 2  |

| 3 | THE    | ORY OF OPERATION                               | 3  |

|   | 3.1 In | ntroduction                                    | 3  |

|   | 3.2 N  | avigation                                      | 3  |

|   | 3.3 SS | SBL                                            | 3  |

|   | 3.4 LI | BL positioning                                 | 4  |

|   | 3.5 SS | SBL and LBL                                    | 4  |

|   | 3.6 Te | elemetry                                       | 4  |

|   | 3.7 Ci | ircuit board identification and main functions | 5  |

| 4 | CON    | NECTIONS                                       | 7  |

| 5 | INTF   | RNAL LAYOUT                                    | 9  |

| 6 |        | CUIT BOARD DESCRIPTIONS                        | 11 |

| Ū |        | eneral                                         | 11 |

|   |        | he backplane                                   | 12 |

|   | 6.2.1  | Board description                              | 12 |

|   | 6.2.2  | Main components                                | 12 |

|   | 6.2.3  | Socket mounted components                      | 12 |

|   | 6.2.4  | Connections                                    | 12 |

|   | 6.2.5  | Pin assignments                                | 13 |

|   | 6.2.6  | Maintenance aids                               | 24 |

|   | 6.3 In | nput-M                                         | 25 |

|   | 6.3.1  | Location and purpose                           | 25 |

|   | 6.3.2  | Physical description                           | 25 |

|   | 6.3.3  | Circuit description                            | 25 |

|   | 6.3.4  | Connections                                    | 27 |

|   | 6.3.5  | Maintenance aids                               | 28 |

|   | 6.4 A  | nalogue digital converter (ADCM)               | 30 |

|   | 6.4.1  | Location and purpose                           | 30 |

|   | 6.4.2  | Physical description                           | 30 |

|   | 6.4.3  | Circuit description                            | 30 |

|   | 6.4.4  | Connections                                    | 31 |

|   | 6.4.5  | Maintenance aids                               | 31 |

| 6.5 Dig  | rital signal processor (DSPM 50)   | 33 |

|----------|------------------------------------|----|

| 6.5.1    | Location and purpose               | 33 |

| 6.5.2    | Physical description               | 33 |

| 6.5.3    | Circuit description                | 33 |

| 6.5.4    |                                    | 35 |

| 6.5.5    | Maintenance aids                   | 35 |

| 6.6 Tra  | nsmitter (TXM)                     | 36 |

| 6.6.1    | Purpose                            | 36 |

| 6.6.2    | Board description                  | 36 |

| 6.6.3    | Front mounted devices              | 36 |

| 6.6.4    | Circuit description                | 36 |

| 6.6.5    | Socket-mounted components          | 37 |

| 6.6.6    |                                    | 37 |

| 6.6.7    | Maintenance aids                   | 38 |

| 6.7 "Po  | werbox" AC power supply            | 39 |

| 6.7.1    | Purpose                            | 39 |

| 6.7.2    | Board description                  | 39 |

| 6.7.3    | Technical specifications           | 39 |

| 6.7.4    | Electrical characteristics         | 39 |

| 6.7.5    | Socket-mounted components          | 39 |

| 6.7.6    | Connections                        | 40 |

| 6.7.7    |                                    | 40 |

| 6.7.8    | LEDs                               | 40 |

| 6.7.9    | Fuses                              | 40 |

| 6.8 Cor  |                                    | 41 |

| 6.8.1    | Location and purpose               | 41 |

| 6.8.2    | Physical description               | 41 |

| 6.8.3    | Circuit description                | 41 |

| 6.8.4    |                                    | 42 |

| 6.8.5    | Maintenance aids                   | 42 |

| 6.9 Inp  | out/output board (IO/M)            | 44 |

| 6.9.1    |                                    | 44 |

| 6.9.2    | Board description                  | 44 |

| 6.9.3    | Front mounted devices              | 44 |

| 6.9.4    | Circuit description                | 44 |

| 6.9.5    | Socket-mounted components          | 45 |

| 6.9.6    | Connections                        | 45 |

| 6.9.7    | Maintenance aids                   | 46 |

| 6.10 The | e responder controller (RPC) board | 47 |

| 6.10.1   | Purpose                            | 47 |

$ext{IV}$

|   | 6.10.2  | Board description                        | 47         |

|---|---------|------------------------------------------|------------|

|   | 6.10.3  | Front mounted devices                    | 47         |

|   | 6.10.4  | Circuit description                      | 47         |

|   | 6.10.5  | Socket-mounted components                | 47         |

|   | 6.10.6  | Connections                              | 47         |

|   | 6.10.7  | Maintenance aids                         | 48         |

|   | 6.11 DC | power supply (DC - PWR)                  | 49         |

|   | 6.11.1  | Purpose                                  | 49         |

|   | 6.11.2  | Board description                        | 49         |

|   | 6.11.3  | Circuit description                      | 49         |

|   | 6.11.4  | Socket-mounted components                | 50         |

|   | 6.11.5  | Connections                              | 50         |

|   | 6.11.6  | Maintenance aids                         | 52         |

| 7 | REPL    | ACEMENT OF PARTS                         | <b>5</b> 3 |

|   | 7.1 Ger | neral                                    | 53         |

|   | 7.2 Rej | placement of circuit boards and software | 53         |

|   | 7.2.1   | Removal of circuit boards                | 53         |

|   | 7.2.2   | Software replacement                     | 54         |

|   | 7.2.3   | Removal of the backplane                 | 55         |

|   | 7.2.4   | Replacement of the backplane             | 56         |

|   | 7.2.5   | Replacement of circuit boards            | 56         |

|   | 7.3 Rej | placement of fuses                       | 57         |

|   | 7.3.1   | Fuse locations                           | 57         |

|   | 7.3.2   | Fuse replacement                         | 57         |

## **Document history**

(The information on this page is for internal use)

- **Rev. A** Original edition based on P2421, document "C", rev. A.

- **Rev. B** Document updated, some unnecessary information removed, some block diagrams added. Document reformatted to Ileaf 6.1.

- **Rev. C** DSPM and CPU pcbs changed. Other minor corrections. Ref. 130512C.

VI 130512/C

# Blank page

#### 1 INTRODUCTION

This technical description is created to assist the maintenance engineer with intermediate level maintenance operations. This means that the maintenance technician or engineer is expected to replace faulty Line Replaceable Units (LRU) (circuit boards or modules), but not to perform circuit board repairs. In order to find the faulty component, it is further expected that the maintenance personnel have access to standard electronic instruments, such as oscilloscopes and multimeters.

The personnel designated to perform maintenance on this unit (and the rest of the system) should be well qualified technical personnel, with experience of computer-based electronic circuitry. It is also strongly recommended that the personnel are familiar with the basic principles of hydroacoustic technology, and in particular, positioning systems.

Training courses are available from Kongsberg Simrad AS.

#### 2 GENERAL INFORMATION

### 2.1 Design

The Transceiver Unit is constructed of aluminium panels and extruded strip. One of several different cover panel designs may be used depending on the type of installation (console, desk-top, rack, or portable). The dismantling procedures described in this manual refer to the unit as used in the console or 19" rack.

The majority of the circuit boards contained in the unit are standard single-Europa cards, accessible by opening the front of the unit. The cards are plug-in units, held in position by plastic clips.

3 mm  $\emptyset$  holes are drilled in the upper and lower front corners of each board. These are to attach the wire handle used to extract the board from the unit.

#### 2.2 Maintenance actions

The corrective maintenance on the Transceiver Unit is limited to operational checks and circuit board replacements. An extension board will be required if the maintenance engineer wishes to perform measurements on the boards during system operation. This is delivered with the standard spare parts kit for the Transceiver Unit.

#### 2.3 External connections

All external connections to the Transceiver Unit are made via plugs located on the rear of the unit. Refer to chapter NO TAG for further information.

### 2.4 Power supply

The Transceiver Unit can be powered from either a 115 Vac or 230 Vac supply. Links must be set inside the unit to adapt the unit to the voltage supply. A mains power switch is located on the front panel, together with a *Power on* indicator lamp.

#### 3 THEORY OF OPERATION

#### 3.1 Introduction

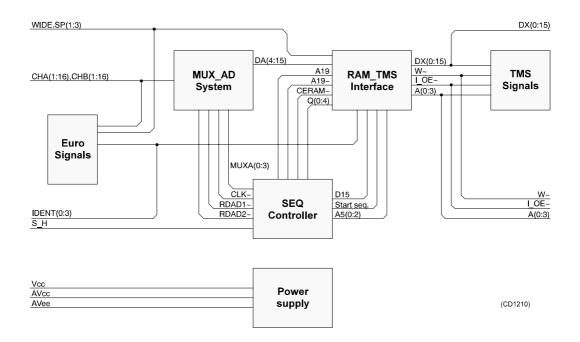

The HPR 400 Transceiver Unit is the central part of the HPR system. It contains the following:

- Electronic circuitry for transmission of acoustic pulses

- Amplifiers and filters for reception of acoustic signals

- Interfaces to external sensors

- Serial line for communication with the Beam Control Unit (for tracking systems)

- Serial line for communication with the System Controller (an Ethernet link will be available shortly).

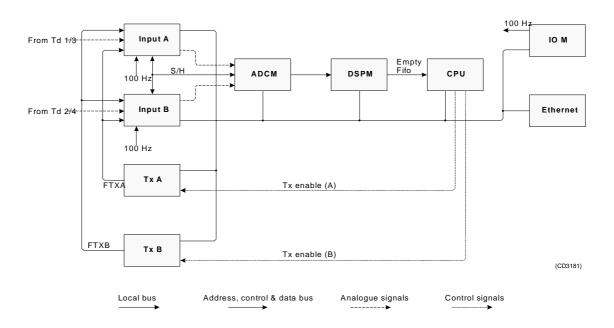

The Transceiver Unit's main navigation function is to interrogate transponders and measure the range and bearing to them. The main telemetry function is to transmit and receive acoustic signals.

### 3.2 Navigation

The operator selects the active mode of operation. The system can then switch automatically between the selected mode and the other available mode(s). This means that the system can make use of several different types of transponder in the same operation.

#### **3.3 SSBL**

In this mode, both direction and range to the transponder(s) are computed.

When a transponder is switched on by the operator, the transceiver will start interrogation using frequencies corresponding to the applicable transponder channel. This is achieved by controlling the transmitter and receiver (preamplifier) boards. The Central Processing Unit (CPUEX) circuit board measures the time elapsed from the interrogation (transmission) till the pulse is detected by the Digital Signal Processor (DSPM) board.

The three "R", "X" and "Y" signals received from the HPR transducer will first enter the Input A or Input B preamplifier circuit boards where they are amplified and filtered. The signals are then sampled and converted to binary format by the Analogue/Digital Converter (ADCM) circuit board. The DSPM 50 reads the data on the ADCM output, detects the signals, and calculates the phase differences between the "R" and "X" input channels and the "R" and "Y" input channels.

The DSPM 50 transfers the received data to the CPUEX circuit board, which then calculates the "X", "Y" and "R" coordinates to the transponder. In this calculation, the data from the external vertical reference unit and compass is used to compensate for the roll and pitch of the vessel. The sensor data is received and converted by the Input Output (IOM) circuit board. When the positioning calculations has been terminated, the current position is sent to the System Controller, and a new interrogation sequence can begin.

### 3.4 LBL positioning

In this mode, only the ranges to the transponders are computed, and several ranges are then used to triangulate the position.

The functional operation is basically the same as for SSBL. However, in the LBL mode the transceiver will await replies from all the transponders in the transponder array before it starts on a new interrogation sequence. The system uses the R channel to detect the range.

#### 3.5 SSBL and LBL

In this mode, both range and direction to the transponder(s) are computed.

This mode is a combination of the SSBL and LBL modes described above, and the functional operation is basically identical to the SSBL. However, the transceiver will await replies from all the transponders in the array before starting a new interrogation sequence.

### 3.6 Telemetry

The operator may select this mode when he/she wishes to send and receive telemetry messages, for example to read the battery status of a transponder. When the transceiver reads the telemetry message from the System Controller, it will convert the message into acoustic signals. This acoustic message contains bursts and pulses with different frequencies and fixed intervals. The transceiver transmits the message(s), and will await the telemetry reply.

The signal path is identical as for navigation mode. The DSPM 50 will calculate the frequency of the current reception, and report this to the CPUEX. The CPUEX will assemble the frequency data, and decode the message from acoustic pulses into digital values. The data is then passed on to the System Controller.

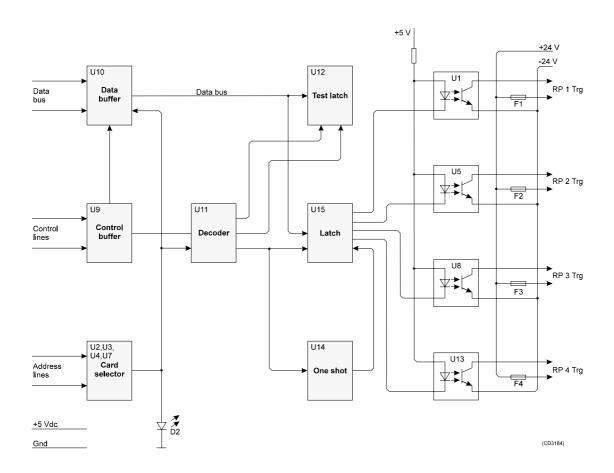

Figure 1 HPR 400 Transceiver unit - functional block diagram

#### 3.7 Circuit board identification and main functions

- Central Processing Unit (CPUEX)

- Position calculation

- Loads and controls the DSPM 50 program

- Serial line to CDU

- Controls Tx/Rx hardware

- Digital Signal Processor (DSPM 50)

- Reads data from ADCM

- Performs pulse detection

- Performs digital filtering (Fast Fourier Transformations)

- Analog Digital Converter (ADCM)

- Samples the data from INPUTM

- Converts to binary format

- Input (INPUTM)

- 8-channel receiver

- Amplifies

- Bandpass filtering

- Sample/hold circuitry

- Transmitter (TXM)

- Transmitter

- Frequency generator for Rx and Tx frequency

#### • Input & Output (IOM)

- Interface to vertical reference unit (analogue)

- Interface to gyro (synchro and serial line)

- TVG initialization

- Clock for phase locked loop on INPUTM

- Ethernet (ENET-M)

- Ethernet interface

- Motherboard

- Connects all the individual circuit boards together

#### 4 CONNECTIONS

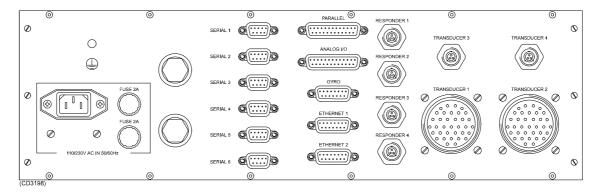

All connections to and from the HPR 400 Transceiver Unit are made on the connection panel on the rear of the unit. All connectors are male except where stated female.

Figure 2 The connectors on the Transceiver Unit's rear panel

This panel holds the following connectors and fuses (top to bottom, left to right when looking at the rear panel):

- 1 Standard 3-pin, 230 Vac, 50/60 Hz mains power in.

- 2 Fuse, 230 Vac, 2 A.

- 3 Fuse, 230 Vac, 2 A.

- 4 9-pin D-connector for Serial line 1.

- 5 9-pin D-connector for <u>Serial line 2</u>.

- 6 9-pin D-connector for <u>Serial line 3</u>.

- 7 9-pin D-connector for <u>Serial line 4</u>.

- 8 9-pin D-connector for <u>Serial line 5</u>.

- 9 9-pin D-connector for Serial line 6.

- 10 25-pin D-connector for <u>Parallel input</u>.

- 11 25-pin D-connector for Analogue input/output.

- 12 15-pin D-connector for Gyro input.

- 13 15-pin D-connector for Ethernet 1.

- 14 15-pin D connector for Ethernet 2.

- 15 3-pin Amphenol connector for <u>Responder 1</u>.

- 16 3-pin Amphenol connector for <u>Responder 2</u>.

- 3-pin Amphenol connector for Responder 3.

- 18 3-pin Amphenol connector for Responder 4.

- 19 3-pin Amphenol connector for <u>Transducer 3</u>.

- 20 3-pin Amphenol connector for <u>Transducer 4</u>.

- 21 35-pin Amphenol connector for <u>Transducer 1</u>.

- 22 35-pin Amphenol connector for <u>Transducer 2</u>.

Note!

The two white plastic caps are the securing nuts for two capacitors located on the inside of the Transceiver Unit rear panel.

All connectors are marked with labels as indicated on the previous drawing.

### **5 INTERNAL LAYOUT**

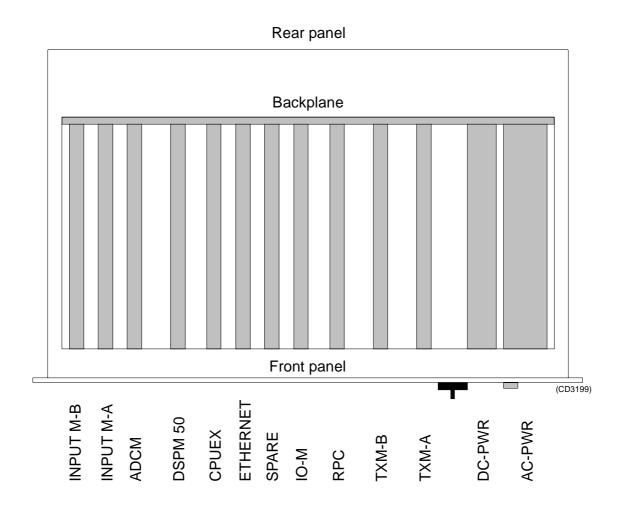

The Transceiver Unit holds the following circuit boards and power units:

From left to right:

- Input M A/B.

- A/D Converter (ADCM).

- Digital Signal Processor (DSPM 50).

- Control Processing Unit (CPUEX).

- Ethernet.

- Spare.

- Input/Output (IOM).

- Responder (RPC) (Option).

- Transmitter (TXM A/B).

- DC Power supply (DC PWR).

- AC Power supply (AC PWR).

The backplane is located behind the circuit boards, and is accessible through the rear of the Transceiver Unit. All the circuit boards and power units must be removed through the front of the unit before the backplane can be removed. All connections to the backplane are made using plugs.

Figure 3 HPR 400 Transceiver Unit - internal layout

## **6 CIRCUIT BOARD DESCRIPTIONS**

#### 6.1 General

This section provides a full functional description of each of the circuit boards contained within the HPR 400 Transceiver Unit. Refer to chapter 3 for a description of the Transceiver Unit's theory of operation.

### 6.2 The backplane

#### 6.2.1 Board description

The backplane is located in the back of the Transceiver Unit. It is the interconnection circuit board, carrying connectors and wiring tracks to interconnect the other circuit boards in the Transceiver Unit. All the other circuit boards plug into the backplane.

#### 6.2.2 Main components

The board holds the following three ICs:

- U01 ... 74HC240 Buffer, inverted on outputs

- U02 .. PAL 20V8 Address decoder. (For TX-PCBs only)

- U03 . . . . 74HC123F Retriggerable monostable multivibrator

#### 6.2.3 Socket mounted components

The board holds only one socket-mounted component:

• U02PAL 20V8 Address decoder. (For TX-PCBs only)

#### 6.2.4 Connections

There are 37 connectors on the circuit board, mounted on both sides. Connectors J1 to J12 are 96-pin Europa connectors for the single Euro-card circuit boards in the unit. For the pin configurations, refer to the following drawing:

|                   | 8                        |

|-------------------|--------------------------|

| HPR 400 Backplane | 824-108544 (SH-067)      |

| J1                | Input-B                  |

| J2                | Input-A                  |

| J3                | ADCM                     |

| J4                | DSPM                     |

| J5                | CPU                      |

| J6                | Ethernet                 |

| J7                | Spare                    |

| J8                | IO-M                     |

| J9                | RPC                      |

| J10               | TXM-B                    |

| J11               | TXM-A                    |

| J12               | POWERM                   |

| P14               | 8-pin Phoenix plug, male |

| P1550-pin 3M, male, flat ribbon cable connector  |

|--------------------------------------------------|

| P1618-pin Molex, male                            |

| P17 8-pin Phoenix plug, male                     |

| P18 2-pin Phoenix plug, male                     |

| P19 2-pin Phoenix plug, male                     |

| P20 2-pin Phoenix plug, male                     |

| P21 34-pin 3M, male, flat ribbon cable connector |

| P22 50-pin 3M, male, flat ribbon cable connector |

| P23 50-pin 3M, male, flat ribbon cable connector |

| P24 2-pin Phoenix plug, male                     |

| P25 2-pin Phoenix plug, male                     |

| P269-pin Molex, male                             |

| P273-pin Molex, male                             |

| P289-pin Molex, male                             |

| P293-pin Molex, male                             |

| P306-pin Molex, male                             |

| P319-pin Molex, male                             |

| P323-pin Molex, male                             |

| P339-pin Molex, male                             |

| P343-pin Molex, male                             |

| P356-pin Molex, male                             |

| P363-pin Molex, male                             |

| P373-pin Molex, male                             |

| P38                                              |

## 6.2.5 Pin assignments

| P14 pin assignments |           |                              |

|---------------------|-----------|------------------------------|

| Pin                 | Signal    | Description                  |

| 1                   | TD 2, Tx+ | Transducer 2, transmission + |

| 2                   | TD 2, Tx  | Transducer 2, transmission – |

| 3                   | TD 4, Tx+ | Transducer 4, transmission + |

| 4                   | TD 4, Tx  | Transducer 4, transmission + |

| 5                   | +15 Vdc   |                              |

| 6                   | -15 Vdc   |                              |

| 7                   | AGND      | Analogue ground              |

| 8                   | DGND      | Digital ground               |

|     | P15 pin assignments         |                                     |   |  |  |

|-----|-----------------------------|-------------------------------------|---|--|--|

| Pin | Pin Signal Description Ext. |                                     |   |  |  |

| 1   | RS422_Rx1                   | RS422+ serial line. To CPU Input    | 1 |  |  |

| 2   | RS422_Tx1-                  | RS422- serial line. From CPU Output | 6 |  |  |

| 3   | RS232_Rx                    | RS232 serial line. To CPU Input     | 2 |  |  |

| 4   |                             |                                     | 7 |  |  |

| 5   | RS232_Tx                    | RS232 serial line. From CPU Output  | 3 |  |  |

| 6   |                             |                                     | 8 |  |  |

| 7   | RS422_Rx1-                  | RS422- serial line. To CPU Input    | 4 |  |  |

| 8   | RS422_Tx1                   | RS422+ serial line. From CPU Output | 9 |  |  |

| 9   | GND1                        | Galvanically isolated ground        | 5 |  |  |

| 10  | RS422_Rx2                   | RS422+ serial line 2                | 1 |  |  |

| 11  | RS422_Tx2-                  | RS422- serial line 2 Output         | 6 |  |  |

| 12  |                             |                                     | 2 |  |  |

| 13  |                             |                                     | 7 |  |  |

| 14  |                             |                                     | 3 |  |  |

| 15  |                             |                                     | 8 |  |  |

| 16  | RS422_Rx2-                  | RS422- serial line 2 Input          | 4 |  |  |

| 17  | RS422_Tx2                   | RS422+ serial line 2 Output         | 9 |  |  |

| 18  | GND                         | Ground                              | 5 |  |  |

| 19  | RS422_Rx3                   | RS422+ serial line 3                | 1 |  |  |

| 20  | RS422_Tx3-                  | RS422- serial line 3 Output         | 6 |  |  |

| 21  |                             |                                     | 2 |  |  |

| 22  |                             |                                     | 7 |  |  |

| 23  |                             |                                     | 3 |  |  |

| 24  |                             |                                     | 8 |  |  |

| 25  | RS422_Rx3-                  | RS422- serial line 3 Input          | 4 |  |  |

| 26  | RS422_Tx3                   | RS422+ serial line 3 Output         | 9 |  |  |

| 27  | GND                         | Ground                              | 5 |  |  |

| 28  | SY1_in                      | External sync1+ Input               | 1 |  |  |

| 29  | SY1_out-                    | External sync1 Output               | 6 |  |  |

| 30  | SY2_out-                    | External sync2 Output               | 2 |  |  |

| 31  | SY2_in                      | External sync2+ Input               | 7 |  |  |

| 32  | SY2_out                     | External sync2+ Output              | 3 |  |  |

| 33  | SY2_in-                     | External sync2 Input                | 8 |  |  |

| 34  | SY1_in-                     | External sync1 Input                | 4 |  |  |

| 35  | SY1_out                     | External sync1+ Output              | 9 |  |  |

| 36  | GND                         | Ground                              | 5 |  |  |

| P15 pin assignments |        |                          |      |

|---------------------|--------|--------------------------|------|

| Pin                 | Signal | Description              | Ext. |

| 37                  | ANA_1  | Analogue 1 Input         | 14   |

| 38                  | AGND   | Analogue ground          | 2    |

| 39                  | ANA_2  | Analogue 2 Input         | 15   |

| 40                  | AGND   | Analogue ground          | 3    |

| 41                  |        |                          | 16   |

| 42                  |        |                          | 4    |

| 43                  |        |                          | 17   |

| 44                  |        |                          | 5    |

| 45                  | S1     | Synchro gyro S1 Input    | 1    |

| 46                  | R.Hi   | Reference high R.HiInput | 9    |

| 47                  | S2     | Synchro gyro S2 Input    | 2    |

| 48                  | R.L    | Reference low R.L Input  | 10   |

| 49                  | S3     | Synchro gyro S3 Input    | 3    |

| 50                  |        |                          | 11   |

Abbreviations: SY = Synch, ANA = Analogue

| P16 pin assignment |                       |  |  |

|--------------------|-----------------------|--|--|

| Pin                | Description           |  |  |

| 1                  | +24 volt, responder 1 |  |  |

| 2                  | Trigger, responder 1  |  |  |

| 3                  | Digital ground        |  |  |

| 4                  | Analogue ground       |  |  |

| 5                  | +24 volt, responder 2 |  |  |

| 6                  | Trigger, responder 2  |  |  |

| 7                  | Digital ground        |  |  |

| 8                  | Analogue ground       |  |  |

| 9                  | +24 volt, responder 3 |  |  |

| 10                 | Trigger, responder 3  |  |  |

| 11                 | Digital ground        |  |  |

| 12                 | Analogue ground       |  |  |

| 13                 | +24 volt, responder 4 |  |  |

| 14                 | Trigger, responder 4  |  |  |

| 15                 | Digital ground        |  |  |

| 16                 | Analogue ground       |  |  |

| 17                 | _                     |  |  |

| 18                 | _                     |  |  |

| P17 pin assignment |           |                              |  |

|--------------------|-----------|------------------------------|--|

| Pin                | Signal    | Description                  |  |

| 1                  | TD 1, Tx+ | Transducer 1, transmission + |  |

| 2                  | TD 1, Tx  | Transducer 1, transmission – |  |

| 3                  | TD 3, Tx+ | Transducer 3, transmission + |  |

| 4                  | TD 3, Tx  | Transducer 3, transmission + |  |

| 5                  | +15 Vdc   |                              |  |

| 6                  | -15 Vdc   |                              |  |

| 7                  | AGND      | Analogue ground              |  |

| 8                  | DGND      | Digital ground               |  |

| P18 pin assignment     |           |                     |  |

|------------------------|-----------|---------------------|--|

| Pin Signal Description |           |                     |  |

| 1                      | TxA CAP + | Capacitor A +48 Vdc |  |

| 2                      | TxA CAP   | Capacitor A 0 V     |  |

| P19 pin assignment |                        |                     |  |  |

|--------------------|------------------------|---------------------|--|--|

| Pin                | Pin Signal Description |                     |  |  |

| 1                  | TxB CAP +              | Capacitor B +48 Vdc |  |  |

| 2                  | TxB CAP                | Capacitor B 0 V     |  |  |

| P20 pin assignment |                              |  |  |

|--------------------|------------------------------|--|--|

| Pin Description    |                              |  |  |

| 1                  | +48 Vdc from AC power supply |  |  |

| 2 Analogue ground  |                              |  |  |

|     | P21 pin assignments |                                   |      |  |

|-----|---------------------|-----------------------------------|------|--|

| Pin | Signal              | Description                       | Ext. |  |

| 1   | RXAI                | RS422+ serial line A Input        | 1    |  |

| 2   | TXA/                | RS422- serial line A Output       | 6    |  |

| 3   | RXA                 | RS232 serial line A Input         | 2    |  |

| 4   | RXCB                | RX clock TTL Input                | 7    |  |

| 5   | TXA                 | RS232 serial line A Output        | 3    |  |

| 6   | CTSA/               | Clear to send A TTL Input         | 8    |  |

| 7   | RXA/                | RS422– serial line A Input        | 4    |  |

| 8   | TXA0                | RS422+ serial line A Output       | 9    |  |

| 9   | GND                 | Ground reference A                | 5    |  |

| 10  | RXBI                | RS422+ serial line B Input        | 1    |  |

| 11  | TXB/                | RS422– serial line B Output       | 6    |  |

| 12  | RXB                 | RS232 serial line B Input         | 2    |  |

| 13  | TXCB                | RX clock TTLInput                 | 7    |  |

| 14  | TXB                 | RS232 serial line B Output        | 3    |  |

| 15  | CTSB/               | Clear to send B TTL Input         | 8    |  |

| 16  | RXB/                | RS422– serial line B Input        | 4    |  |

| 17  | TXB0                | RS422+ serial line B Output       | 9    |  |

| 18  | GND                 | Ground reference B                | 5    |  |

| 19  | IO1                 | Digital input/output Input/Output | 1    |  |

| 20  | IO2                 | Digital input/output Input/Output | 2    |  |

| 21  | IO3                 | Digital input/output Input/Output | 3    |  |

| 22  | IO4                 | Digital input/output Input/Output | 4    |  |

| 23  | IO5                 | Digital input/output Input/Output | 5    |  |

| 24  | 106                 | Digital input/output Input/Output | 6    |  |

| 25  | 107                 | Digital input/output Input/Output | 7    |  |

| 26  | 108                 | Digital input/output Input/Output | 8    |  |

| 27  | RXCB                | RX clock TTL Input                | 9    |  |

| 28  | TXCB                | TX clock TTL Input                | 10   |  |

| 29  | CTSB/               | Clear to send B TTL Input         | 11   |  |

| 30  | CTSA/               | Clear to send A TTL Input         | 12   |  |

| 31  | GND                 | Power ground                      | 13   |  |

| 32  | GND                 | Power ground                      | 14   |  |

| 33  | +5 Vdc              | +5 Vdc power supply Output        | 15   |  |

| 34  | +5 Vdc              | +5 Vdc power supply Output        | 16   |  |

|     | P22 pin assignments |                                     |   |  |

|-----|---------------------|-------------------------------------|---|--|

| Pin | Signal Description  |                                     |   |  |

| 1   | RS422_Rx1           | RS422+ serial line. To CPU Input    | 1 |  |

| 2   | RS422_Tx1-          | RS422- serial line. From CPU Output | 6 |  |

| 3   | RS232_Rx            | RS232 serial line. To CPU Input     | 2 |  |

| 4   |                     |                                     | 7 |  |

| 5   | RS232_Tx            | RS232 serial line. From CPU Output  | 3 |  |

| 6   |                     |                                     | 8 |  |

| 7   | RS422_Rx1-          | RS422- serial line. To CPU Input    | 4 |  |

| 8   | RS422_Tx1           | RS422+ serial line. From CPU Output | 9 |  |

| 9   | GND1                | Galvanically isolated ground        | 5 |  |

| 10  | RS422_Rx2           | RS422+ serial line 2                | 1 |  |

| 11  | RS422_Tx2-          | RS422– serial line 2 Output         | 6 |  |

| 12  |                     |                                     | 2 |  |

| 13  |                     |                                     | 7 |  |

| 14  |                     |                                     | 3 |  |

| 15  |                     |                                     | 8 |  |

| 16  | RS422_Rx2-          | RS422- serial line 2 Input          | 4 |  |

| 17  | RS422_Tx2           | RS422+ serial line 2 Output         | 9 |  |

| 18  | GND                 | Ground                              | 5 |  |

| 19  | RS422_Rx3           | RS422+ serial line 3                | 1 |  |

| 20  | RS422_Tx3-          | RS422– serial line 3 Output         | 6 |  |

| 21  |                     |                                     | 2 |  |

| 22  |                     |                                     | 7 |  |

| 23  |                     |                                     | 3 |  |

| 24  |                     |                                     | 8 |  |

| 25  | RS422_Rx3-          | RS422- serial line 3 Input          | 4 |  |

| 26  | RS422_Tx3           | RS422+ serial line 3 Output         | 9 |  |

| 27  | GND                 | Ground                              | 5 |  |

| 28  | SY1_in              | External sync1+ Input               | 1 |  |

| 29  | SY1_out-            | External sync1 Output               | 6 |  |

| 30  | SY2_out-            | External sync2 Output               | 2 |  |

| 31  | SY2_in              | External sync2+ Input               | 7 |  |

| 32  | SY2_out             | External sync2+ Output              | 3 |  |

| 33  | SY2_in-             | External sync2 Input                | 8 |  |

| 34  | SY1_in-             | External sync1 Input                | 4 |  |

| 35  | SY1_out             | External sync1+ Output              | 9 |  |

| 36  | GND                 | Ground                              | 5 |  |

|     | P22 pin assignments     |                             |      |  |  |

|-----|-------------------------|-----------------------------|------|--|--|

| Pin | n Signal Description Ex |                             | Ext. |  |  |

| 37  | RXBI                    | RS422+ serial line B Input  | 1    |  |  |

| 38  | TXB/                    | RS422– serial line B Output | 6    |  |  |

| 39  | RXB                     | RS232 serial line B Input   | 2    |  |  |

| 40  | TXCB                    | RX clock TTL Input          | 7    |  |  |

| 41  | TXB                     | RS232 serial line B Output  | 3    |  |  |

| 42  | CTSB/                   | Clear to send B TTL Input   | 8    |  |  |

| 43  | RXB/                    | RS422– serial line B Input  | 4    |  |  |

| 44  | TXB0                    | RS422+ serial line B Output | 9    |  |  |

| 45  | GND                     | Ground reference B          | 5    |  |  |

| 46  |                         |                             |      |  |  |

| 47  |                         |                             |      |  |  |

| 48  |                         |                             |      |  |  |

| 49  |                         |                             |      |  |  |

| 50  |                         |                             |      |  |  |

**Pins 1 through 9** will connect to the external plug Serial I, on backplane (from IOM, P2 pins  $1\rightarrow 9$  P15 pins  $1\rightarrow 9$ ).

**Pins 10 through 18** will connect to the external plug Serial II, on backplane (from IOM, P2 pins  $10\rightarrow18$  P15 pins  $10\rightarrow18$ ).

**Pins 19 through 27** will connect to the external plug Serial III, on backplane (from IOM, P2 pins 19→27 P15 pins 19→27).

**Pins 28 through 36** will connect to the external plug Serial IV, on backplane (from IOM, P2 pins 28→36 P15 pins 28→36).

**Pins 37 through 45** will connect to the external plug Serial V, on backplane (from CPU, P2 pins 10→19 P21 pins 10→19).

**Pins 46 through 50** will connect to the external plug Serial VI (Debug), on backplane (from CPU, P2).

| P23 pin assignments |                           |     |                  |  |

|---------------------|---------------------------|-----|------------------|--|

| Pin                 | Description               | Pin | Description      |  |

| 1                   | IO5, Digital input/output | 26  | GND              |  |

| 2                   | IO6, Digital input/output | 27  | PC0 (Analogue 1) |  |

| 3                   | IO7, Digital input/output | 28  | PC1 (Ground)     |  |

| 4                   | IO8, Digital input/output | 29  | PC2 (Analogue 2) |  |

| 5                   | CLK 0                     | 30  | PC3 (Ground)     |  |

| 6                   | GATE 1                    | 31  | PC4 (Analogue 3) |  |

| 7                   | T0 out                    | 32  | PC5 (Ground)     |  |

| 8                   | T1 out                    | 33  | PC6 (Analogue 4) |  |

| 9                   | GND                       | 34  | PC7 (Ground)     |  |

| 10                  | PB7                       | 35  | GND              |  |

|     | P23 pin assignments |     |                           |  |  |

|-----|---------------------|-----|---------------------------|--|--|

| Pin | Description         | Pin | Description               |  |  |

| 11  | PB6                 | 36  | DIFF 1- (S1, synchro)     |  |  |

| 12  | PB5                 | 37  | DIFF 1 (Rh, ref. high)    |  |  |

| 13  | PB4                 | 38  | DIFF 2- (S2, synchro)     |  |  |

| 14  | PB3                 | 39  | DIFF 2 (Rl, ref. low)     |  |  |

| 15  | PB2                 | 40  | DIFF 3- (S3 synchro)      |  |  |

| 16  | PB1                 | 41  | DIFF 3                    |  |  |

| 17  | PB0                 | 42  | GND                       |  |  |

| 18  | PA7                 | 43  | AN_IN 8 (VRU +15 V)       |  |  |

| 19  | PA6                 | 44  | AN_IN 7 (Analogue ground) |  |  |

| 20  | PA5                 | 45  | AN_IN 6 (VRU –15 V)       |  |  |

| 21  | PA4                 | 46  | AN_IN 5 (Roll)            |  |  |

| 22  | PA3                 | 47  | AN_IN 4 (Common)          |  |  |

| 23  | PA2                 | 48  | AN_IN 3 (Pitch)           |  |  |

| 24  | PA1                 | 49  | AN_IN 2 (Analogue ground) |  |  |

| 25  | PA0                 | 50  | AN_IN 1                   |  |  |

| Signal descriptions for P23 |             |            |            |                     |  |

|-----------------------------|-------------|------------|------------|---------------------|--|

| Signal                      | From        | Via        | Via        | То                  |  |

| Analogue 1                  | IO/M P2 37  | P15 pin 37 | P23 pin 27 | ANALOGUE I/O pin 14 |  |

| GND                         | IO/M P2 38  | P15 pin 38 | P23 pin 28 | ANALOGUE I/O pin 2  |  |

| Analogue 2                  | IO/M P2 39  | P15 pin 39 | P23 pin 29 | ANALOGUE I/O pin 15 |  |

| GND                         | IO/M P2 40  | P15 pin 40 | P23 pin30  | ANALOGUE I/O pin 3  |  |

| S1                          | IO/M P2 45  | P15 pin 45 | P23 pin36  | GYRO pin 1          |  |

| Rh                          | IO/M P2 46  | P15 pin 46 | P23 pin37  | GYRO pin 9          |  |

| S1                          | IO/M P2 47  | P15 pin 47 | P23 pin38  | GYRO pin 2          |  |

| R1                          | IO/M P2 48  | P15 pin 48 | P23 pin39  | GYRO pin 10         |  |

| S3                          | IO/M P2 49  | P15 pin 49 | P23 pin40  | GYRO pin 3          |  |

| VRU +15 Vdc                 | IO/M P1 c23 | P23 pin 43 |            | ANALOGUE I/O pin 22 |  |

| GND                         | IO/M P1 b2  | P23 pin 44 |            | ANALOGUE I/O pin 10 |  |

| VRU –15 Vdc                 | IO/M P1 a2  | P23 pin 45 |            | ANALOGUE I/O pin 23 |  |

| Roll                        | IO/M P1 c22 | P23 pin 46 |            | ANALOGUE I/O pin 11 |  |

| Common                      | IO/M P1 b2  | P23 pin 47 |            | ANALOGUE I/O pin 24 |  |

| Pitch                       | IO/M P1 a2  | P23 pin 48 |            | ANALOGUE I/O pin 12 |  |

| Analogue ground             | IO/M P1 c21 | P23 pin 49 |            | ANALOGUE I/O pin 25 |  |

| P24 pin assignment (DC input) |                |  |  |

|-------------------------------|----------------|--|--|

| Pin Description               |                |  |  |

| 1                             | +48 Vdc backup |  |  |

| 2 Analogue ground             |                |  |  |

| P25 pin assignment (External responder power) |              |                 |  |  |

|-----------------------------------------------|--------------|-----------------|--|--|

| Pin Signal Description                        |              |                 |  |  |

| 1                                             | Ext. pwr RSP | Responder power |  |  |

| 2                                             | AGND         | Analogue ground |  |  |

| P26 pin assignment (To Input-A pcb, channels 1 - 3) |          |                         |  |

|-----------------------------------------------------|----------|-------------------------|--|

| Pin                                                 | Signal   | Description             |  |

| 1                                                   | A INA_1  | Input A, channel 1 IN + |  |

| 2                                                   | A INBA_1 | Input A, channel 1 IN – |  |

| 3                                                   | AGND     | Analogue ground         |  |

| 4                                                   | A INA_2  | Input A, channel 2 IN + |  |

| 5                                                   | A INB_2  | Input A, channel 2 IN – |  |

| 6                                                   | AGND     | Analogue ground         |  |

| 7                                                   | A INA_3  | Input A, channel 3 IN + |  |

| 8                                                   | A INB_3  | Input A, channel 3 IN – |  |

| 9                                                   | AGND     | Analogue ground         |  |

| P27 pin assignment (To Input-A pcb, channel 4) |         |                         |  |

|------------------------------------------------|---------|-------------------------|--|

| Pin Signal Description                         |         |                         |  |

| 1                                              | A INA_4 | Input A, channel 4 IN + |  |

| 2                                              | A INB_4 | Input A, channel 4 IN – |  |

| 3                                              | AGND    | Analogue ground         |  |

| P28 pin assignment (To Input-A pcb, channels 5 - 7) |         |                         |

|-----------------------------------------------------|---------|-------------------------|

| Pin                                                 | Signal  | Description             |

| 1                                                   | A INA_5 | Input A, channel 5 IN + |

| 2                                                   | A INB_5 | Input A, channel 5 IN – |

| 3                                                   | AGND    | Analogue ground         |

| 4                                                   | A INA_6 | Input A, channel 6 IN + |

| 5                                                   | A INB_6 | Input A, channel 6 IN – |

| 6                                                   | AGND    | Analogue ground         |

| 7                                                   | A INA_7 | Input A, channel 7 IN + |

| 8                                                   | A INB_7 | Input A, channel 7 IN – |

| 9                                                   | AGND    | Analogue ground         |

| P29 pin assignment (To Input-A pcb, channel 8) |         |                         |

|------------------------------------------------|---------|-------------------------|

| Pin Signal Description                         |         |                         |

| 1                                              | A INA_8 | Input A, channel 8 IN + |

| 2                                              | A INB_8 | Input A, channel 8 IN – |

| 3                                              | AGND    | Analogue ground         |

| P30 pin assignment (For transducer 1) |             |                         |

|---------------------------------------|-------------|-------------------------|

| Pin                                   | Signal      | Description             |

| 1                                     | ST 24, VC_B | Voltage control B, Td 1 |

| 2                                     | DGND        | Digital ground          |

| 3                                     | AGND        | Analogue ground         |

| 4                                     | N/W-signal  | Narrow/Wide Td 1        |

| 5                                     | AGND        | Analogue ground         |

| 6                                     | Screen      |                         |

|     | P31 pin assignment (To Input-B pcb, channels 1 - 3) |                         |  |

|-----|-----------------------------------------------------|-------------------------|--|

| Pin | Signal                                              | Description             |  |

| 1   | B INA_1                                             | Input B, channel 1 IN + |  |

| 2   | B INBA_1                                            | Input B, channel 1 IN – |  |

| 3   | AGND                                                | Analogue ground         |  |

| 4   | B INA_2                                             | Input B, channel 2 IN + |  |

| 5   | B INB_2                                             | Input B, channel 2 IN – |  |

| 6   | AGND                                                | Analogue ground         |  |

| 7   | B INA_3                                             | Input B, channel 3 IN + |  |

| 8   | B INB_3                                             | Input B, channel 3 IN – |  |

| 9   | AGND                                                | Analogue ground         |  |

| P32 pin assignment (To Input-B pcb, channel 4) |         |                         |

|------------------------------------------------|---------|-------------------------|

| Pin Signal Description                         |         |                         |

| 1                                              | B INA_4 | Input B, channel 4 IN + |

| 2                                              | B INB_4 | Input B, channel 4 IN – |

| 3                                              | AGND    | Analogue ground         |

| P33 pin assignment (To Input-B pcb, channels 5 - 7) |         |                         |

|-----------------------------------------------------|---------|-------------------------|

| Pin                                                 | Signal  | Description             |

| 1                                                   | B INA_5 | Input B, channel 5 IN + |

| 2                                                   | B INB_5 | Input B, channel 5 IN – |

| 3                                                   | AGND    | Analogue ground         |

| 4                                                   | B INA_6 | Input B, channel 6 IN + |

| 5                                                   | B INB_6 | Input B, channel 6 IN – |

| 6                                                   | AGND    | Analogue ground         |

| 7                                                   | B INA_7 | Input B, channel 7 IN + |

| 8                                                   | B INB_7 | Input B, channel 7 IN – |

| 9                                                   | AGND    | Analogue ground         |

| P34 pin assignment (To Input-A pcb, channel 8) |         |                         |

|------------------------------------------------|---------|-------------------------|

| Pin Signal Description                         |         |                         |

| 1                                              | B INA_8 | Input B, channel 8 IN + |

| 2                                              | B INB_8 | Input B, channel 8 IN – |

| 3                                              | AGND    | Analogue ground         |

| P35 pin assignment (For transducer 2) |             |                         |

|---------------------------------------|-------------|-------------------------|

| Pin                                   | Signal      | Description             |

| 1                                     | ST 25, VC_D | Voltage control D, Td 2 |

| 2                                     | DGND        | Digital ground          |

| 3                                     | AGND        | Analogue ground         |

| 4                                     | N/W-signal  | Narrow/Wide Td 2        |

| 5                                     | AGND        | Analogue ground         |

| 6                                     | Screen      |                         |

| P36 pin assignment (For transducer 3) Note! External cable from P36 to Input-A pcb, channel 8 |         |                               |

|-----------------------------------------------------------------------------------------------|---------|-------------------------------|

| Pin Signal Description                                                                        |         |                               |

| 1                                                                                             | ALNK_A1 | Telemetry (+) TxMB to input A |

| 2                                                                                             | ALNK_A2 | Telemetry (-) TxMB to input A |

| 3                                                                                             | AGND    | Analogue ground               |

| P37 pin assignment (For transducer 4) Note! External cable from P36 to Input-B pcb, channel 8 |         |                               |

|-----------------------------------------------------------------------------------------------|---------|-------------------------------|

| Pin Signal Description                                                                        |         |                               |

| 1                                                                                             | ALNK_B1 | Telemetry (+) TxMB to input B |

| 2                                                                                             | ALNK_B2 | Telemetry (-) TxMB to input B |

| 3                                                                                             | AGND    | Analogue ground               |

| P38 pin assignment     |               |               |

|------------------------|---------------|---------------|

| Pin Signal Description |               |               |

| 1                      | "ON", (diode) | Power ON      |

| 2                      | GND           | Ground        |

| 3                      | "CPU" (diode) | Not connected |

## 6.2.6 Maintenance aids

#### 6.2.6.1 Links

| LK 1          | . $0 \text{ V}$ for responder power. Link <b>IN</b> means internal power |

|---------------|--------------------------------------------------------------------------|

| LK 2 4        | +48 V for responder power. Link <b>IN</b> means internal power           |

| ST 1          | Link 1-2 for VC_B to Input-A P1 c7                                       |

| ST 1          | Link 2–3 for VC_A to Input-A P1 c7 (Normally closed)                     |

|               | Seen from rear:                                                          |

|               |                                                                          |

| ST 2          | Link 1-2 for VC_D to Input-B P1 c7                                       |

| ST 2          | Link 2–3 for VC_C to Input-B P1 c7 (Normally closed)                     |

|               | Seen from rear:                                                          |

| ST 7          | EXRDY- Normally out                                                      |

|               |                                                                          |

|               | _ ` ` '                                                                  |

| ST25          | VC_D, (TVG), TD2. Normally in                                            |

| ST26          | Link 1–2 for VEE(–5 V) to Input A/B P1 abc 28                            |

| ST26 Link 2–3 | for VCC(+5 V) to Input-A/B P1 abc 28 (Normally closed)                   |

|               | Seen from rear:                                                          |

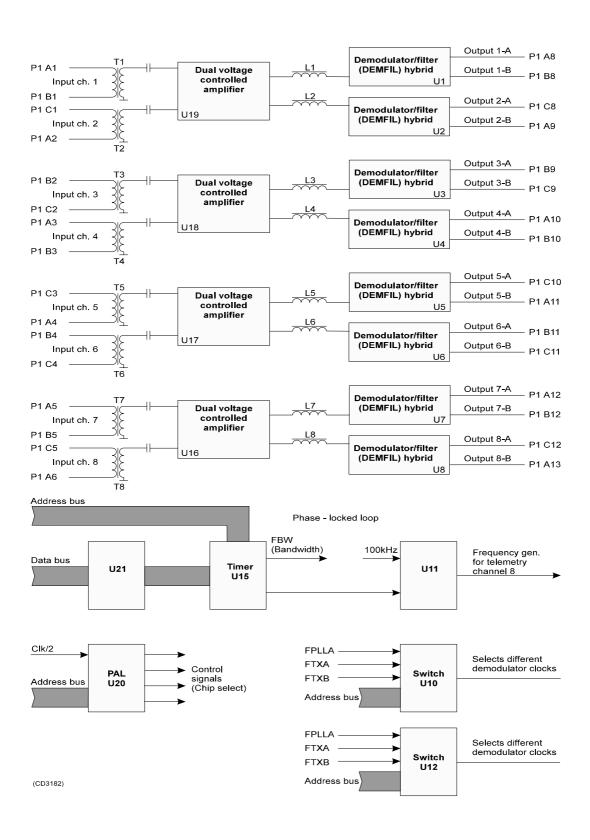

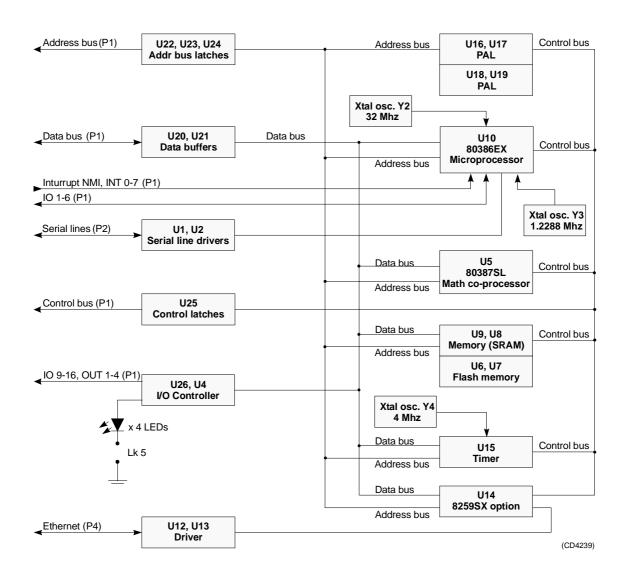

### 6.3 Input-M

#### 6.3.1 Location and purpose

The HPR 400 Transceiver Unit holds two Input–M boards, B and A. These are located in the rack in the first and second slots from the left respectively. The purpose of the Input–M circuit board is to amplify transducer signals, perform demodulation and narrow band filtering, and present the output signals via Sample and hold circuitry.

#### 6.3.2 Physical description

The Input-M board is a single Euro-card circuit board.

#### 6.3.3 Circuit description

The Input–M circuit board is designed for eight individual channels, using identical analogue channel hybrid circuits. However, only five are fitted. The first four (grouped) are used for the SSBL system, the fifth (set apart from the others) is for the LBL system. The board is also equipped with digital circuitry common to all the analogue channels.

The circuit board's eight inputs from the transducer(s) are balanced, and individual input transformers are implemented. Each channel has a broad-band amplifier with voltage-controlled gain. The maximum gain is 75 dB relative to 1 V. If the transducer has its own internal amplifier, the signals may be routed directly to the filters by hardware straps.

The demodulators operate either with a common modulator frequency, with a common frequency for each of the two groups, or with an external frequency. The frequency is generated on the Input–M board, but it is controlled by the Central Processing Unit (CPU) board.

The low pass filters operate with a pass-band. The filters are controlled by a clock on the board, which in turn is controlled by the CPU. All the filters operate with the same bandwidth.

The outputs from each channel are the sine and cosine (real and imaginary) vectors of the demodulated signals. The analogue range is 0 to  $\pm 2.5$  Vdc. All the outputs are sampled by an external sample signal, and the values are stored until the next sample command arrives.

There are two frequency generators for the demodulators. They operate at 4 times the signal frequency, in steps of 100 Hz.

Figure 4 The Input M A/B circuit board - block diagram

#### 6.3.4 Connections

The Input-M board carries one connector. This is a 96-pin Europa connector mounted on the rear edge of the board, used to link the board into the backplane.

| P1 pin assignment<br>96-pin Europa connector |          |          |          |

|----------------------------------------------|----------|----------|----------|

| Pin                                          | A        | В        | C        |

| 1                                            | IN1-A    | IN1-B    | IN2-A    |

| 2                                            | IN2-B    | IN3-A    | IN3-B    |

| 3                                            | IN4–A    | IN4-B    | IN5-A    |

| 4                                            | IN5-B    | IN6-A    | IN6-B    |

| 5                                            | IN7–A    | IN7-B    | IN8-A    |

| 6                                            | IN8-B    |          |          |

| 7                                            | VCA      |          | VCB      |

| 8                                            | OUT1-A   | OUT1-B   | OUT2-A   |

| 9                                            | OUT2-B   | OUT3-A   | OUT3-B   |

| 10                                           | OUT4-A   | OUT4-B   | OUT5-A   |

| 11                                           | OUT5-B   | OUT6-A   | OUT6-B   |

| 12                                           | OUT7-A   | OUT7-B   | OUT8-A   |

| 13                                           | OUT8-B   | TX_EN B~ | TX_EN A~ |

| 14                                           | RESET_IN |          | CLK/2    |

| 15                                           | 100 Hz   |          | RESET    |

| 16                                           | FTX A    | FTX B    | F IN     |

| 17                                           | D0       | D1       | D2       |

| 18                                           | D3       | D4       | D5       |

| 19                                           | D6       | D7       |          |

| 20                                           | A01      | A02      |          |

| 21                                           | A16      |          | A06      |

| 22                                           | A07      | A08      | A09      |

| 23                                           | A10      | A11      | A12      |

| 24                                           | A13      | A14      | A15      |

| 25                                           | S/H IN   |          |          |

| 26                                           | XIOW     | RESET    | XIOR     |

| 27                                           | AVEE     | AVEE     | AVEE     |

| 28                                           | AVCC     | AVCC     | AVCC     |

| 29                                           | AGND     | AGND     | AGND     |

| 30                                           |          |          |          |

| 31                                           | GND      | GND      | GND      |

| 32                                           | VCC      | VCC      | VCC      |

| P1 Signal descriptions:                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN1–A to IN8–B $\ldots$ Input channels from transducers                                                                                                                                                                                         |

| OUT1-A to OUT8-B Output to ACM PCB                                                                                                                                                                                                              |

| VCA Voltage Control A from IO/M PCB                                                                                                                                                                                                             |

| VCB Voltage Control B from IO/M PCB                                                                                                                                                                                                             |

| TX_EN A~ Transmit Enable A from CPU                                                                                                                                                                                                             |

| TX_EN B~ Transmit Enable B from CPU                                                                                                                                                                                                             |

| RESET IN Not used                                                                                                                                                                                                                               |

| CLK/2 Clock input to PAL from CPU                                                                                                                                                                                                               |

| 100 Hz $$ Modulation frequency from IO/M                                                                                                                                                                                                        |

| RESET From CPU – resets DEMFIL circuit                                                                                                                                                                                                          |

| FTX A Transmitter frequency from TxMA                                                                                                                                                                                                           |

| FTX B Transmitter frequency from TxMB                                                                                                                                                                                                           |

| F IN Bandwidth via U15 to DEMFIL                                                                                                                                                                                                                |

| D0 to D7 8-bit data bus                                                                                                                                                                                                                         |

| A01 to A16                                                                                                                                                                                                                                      |

| $\ensuremath{S}/\ensuremath{H}\text{-}\ensuremath{IN}$ Sample and hold from ADCM                                                                                                                                                                |

| XIOW                                                                                                                                                                                                                                            |

| XIOR I/O read strobe                                                                                                                                                                                                                            |

| AVEE Analogue –5 Vdc                                                                                                                                                                                                                            |

| AVCC Analogue +5 Vdc                                                                                                                                                                                                                            |

| GND Ground                                                                                                                                                                                                                                      |

| VCC Digital +5 Vdc                                                                                                                                                                                                                              |

| 6.3.5 Maintenance aids                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                 |

| 6.3.5.1 Test points                                                                                                                                                                                                                             |

| TP 1 Transducer signal channel 1, (X)                                                                                                                                                                                                           |

| TP 2 Transducer signal channel 2, (Y)                                                                                                                                                                                                           |

| TP 3 Transducer signal channel 3, (R)                                                                                                                                                                                                           |

| TP 4 Same as channel 3. linked together on input                                                                                                                                                                                                |

| TP 5 Not fitted                                                                                                                                                                                                                                 |

| TP 6 Not fitted                                                                                                                                                                                                                                 |

| TP 7 Not fitted                                                                                                                                                                                                                                 |

| TP 8 Transducer signal channel 8 (Telemetry)                                                                                                                                                                                                    |

| • The demodulator frequency should be present at "Demfil" pins 1 and 2. The frequency should be two times the actual listening frequency. Note that the frequency will shift by the transmitter pulse after the reply is received. (50 Hz off). |

- The bandwidth clock should be present on "Demfil" pin 14, and should be 50 times the actual bandwidth.

- The Sample/Hold clock should be present on U13 pin 13, and then go to pin 15 on all the "Demfil" packages.

The signal reply pulses (5 to 7 Vp–p) should be present on the test points in front of the "Demfils". (TPs 1, 2, 3, 4 and 8).

• The signal pulse envelope should be present on "Demfil" pins 27 and 28. Maximum amplitude should be 4 V p-p.

#### 6.3.5.2 Links

• LK1

|             | Not used x mod. freq. telemetry normally closed                            |

|-------------|----------------------------------------------------------------------------|

| • LK2       |                                                                            |

|             |                                                                            |

| • LK3       |                                                                            |

|             |                                                                            |

| • LK4 / LK5 |                                                                            |

| Link 1-2    | Lk 4 pin 2 is linked to Lk 5 pin 2 to set bandwidth for wide and telemetry |

# 6.4 Analogue digital converter (ADCM)

### 6.4.1 Location and purpose

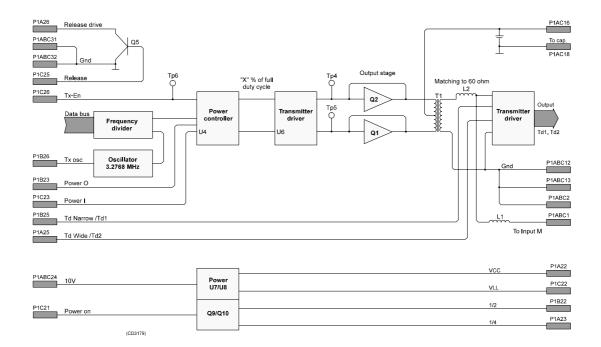

The Analogue Digital Converter (ADCM) circuit board is located in the third slot from the left. The purpose of the ADCM is to perform analogue to digital conversion. It offers conversion of 32 analogue input channels and temporary storage of data in dual port RAM. Up to eight conversion sequences can be programmed into an EPROM. Data sets are stored alternately in two banks of RAM.

# 6.4.2 Physical description

The ADCM is designed to the single Euro-card circuit board standard, with four layers. Two layers are used for the signals, two layers are used for the power supply. The board is equipped with two connectors, one located at each end. A 50-pin connector (P2) is the only front mounted device visible when the board is in position in the HPR 400 Transceiver Unit.

# 6.4.3 Circuit description

The ADCM circuit board provides 32 multiplexed analogue input channels. Dual 16-bit multiplexers are used to select analogue input signals obtained from the sample-and-hold outputs of the Input-M circuit board. Each output from the Input-M provides a real and imaginary analogue signal between  $\pm 2.5$  Vdc.

Real and imaginary inputs to the board are connected to two separate multiplexers. The input channels are selected by the multiplexer address lines. An amplifier system is used between each multiplexer and corresponding A/D converter to create a 0 to +5 V input signal range to the A/D from the  $\pm 2.5 \mathrm{V}$  signal at the multiplexer input. The 12-bit A/Ds are both controlled by the sequence controller.

The conversions take place simultaneously to provide the shortest possible conversion time for two input signals. However, each A/D is started individually.

The digital outputs from the A/Ds are stored in dual port RAM. A full data set (data from conversion of all 32 input signals) is stored alternately in the two banks to allow the last converted data set to be read from the RAM whilst a new set of conversions is in progress.

Note!

The maximum time required to convert one data set (all 32 input signals) is 80 µs. This does not include the 4 µs settling time required in sample-and-hold circuits of the DEMFIL devices.

A 16-bit bi-directional data bus interfaces the ADCM with the other circuit boards.

Figure 5 A / D Converter (ADCM) - block diagram

The control lines IDENT(0:3) provide the board with a unique identification code which is set by jumpers S1 - S4. The external address lines A(0:3) must match this code to select the board.

#### 6.4.4 Connections

The board carries two connectors, one located at each end of the board. **P1** is a 96-pin, male, right-angled connector. It connects the ADCM into the motherboard. **P2** is a 50-pin, male, right-angled connector with ejector/latch. It is located on the front edge of the board.

#### 6.4.5 Maintenance aids

### 6.4.5.1 Test points

| TP 1 | ADC, IC4 input (real signal)        |

|------|-------------------------------------|

| TP 2 | ADC, IC4 BUSY~                      |

| TP 3 | ADC, IC8 input (imaginary signal)   |

| TP 4 | ADC, IC8 BUSY~                      |

| TP 5 | START_SEQ                           |

| TP 6 |                                     |

| TP 7 | IC21 CK (multiplexer address latch) |

| TP 8                | S_H   |

|---------------------|-------|

| TP 9 +5 Vdc di      | gital |

| TP 10               | GND   |

| TP 11 +12 Vdc analo | ogue  |

| TP 12 Analogue gro  | und   |

| TP 1312 Vdc analo   | ogue  |

# 6.5 Digital signal processor (DSPM 50)

### 6.5.1 Location and purpose

The Digital Signal Processor (DSPM 50) board is located fourth from the left in the HPR 400 Transceiver Unit rack. It is designed as a general purpose single board computer, and its main task is to perform digital signal processing.

# 6.5.2 Physical description

The DSPM 50 is a single euro-card circuit board, constructed of eight layers. It holds two LEDs and one 50-pin connector, P2, on its front edge.

### 6.5.3 Circuit description

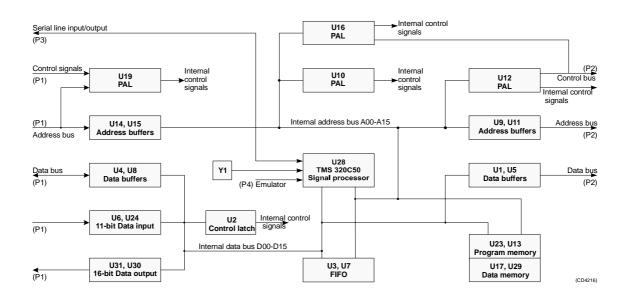

The DSPM 50 is a general purpose digital signal processor board. It utilizes the TMS 320C50 Digital Signal Processor manufactured by Texas Instruments. The DSPM 50 operates on a 50 MHz clock frequency, and holds a total of 128 kbyte memory for program and data storage. The program memory is loaded from a main control processor unit (the Central Processing Unit (CPUEX)) through a general bus interface in the 96-pin Europa connector P1.

The processed output from the DSPM 50 is sent through a FIFO (first in / first out) connected to this bus. External input and output signals are connected to the board through the DSPM 50's I/O expansion bus available on the front mounted 50-pin flat ribbon cable connector P2.

The DSPM 50 board comprises the following functional modules:

- Digital Signal Processor

- Memory

- I/O Expansion Bus

- FIFO Buffer

- 11 Digital Inputs

- 16 Digital Outputs

- Control circuitry

- Bus Interface

- Power +5 Vdc (250 mA typical)

The Texas Instrument signal processor is a fixed point 16-bit processor with a 16-bit address bus. The DSPM 50 has separate program and data addressing space.

Figure 6 Digital Signal Processor (DSPM 50) - block diagram

U13 and U23 are the program memory units, and U17 and U29 are the data memory. Both memories can be read or written to from an external computer.

The signals from the TMS320C50 and the PAL U10 supply all the control signals to the memories. U10 also controls the memory when a external computer is controlling the board, and the external computer can take control of the address bus by buffers U14 and U15. U4 and U8 are the data buffers transceivers. U19 decodes the external computer address bus and read write signals, and generates control signals (SEL1, SEL2, MWR/ and MRD/) to U10 to control the memory. U19 also supplies the latch signal to the control latch U2, and the read signal to the FIFO's U3 and U7. U19 also controls the enabling of the bus buffers and the direction of the data buffer transceivers.